Are FPGAs the Future for the Control of Power Electronics and Motor Drives?

Embedded platforms fight to the bitter end...

I would like to think a bit differently in this post. While the majority of my previous posts were revolving about control theory and circuits (which have been virtually the same for decades), I have not yet addressed the topic of control implementation. So how would one go about implementing some fancy power conversion control schemes?

- Use an integrated chip (=ASIC) made by Texas Instruments, Linear Technology, Microchip, ... Yes, this will work for the overwhelming majority of power converters but not so much for advanced motor drive algorithms (DTC, FOC, estimators, ...).

- Use an 8-bit microcontroller by Microchip. Well, those are very cheap. You can get them for 20c at large quantities. They feature (typically 10-bit) ADC, some PWM modules, typically a 32 MHz oscillator, etc. These ones are fine for some fancy novel power converters as well. Still not enough horsepower for advanced digital power processing or motor control.

- Use a dsPIC (by Microchip - digital signal controller), or even better, use a C2000 series (TI) microcontroller . So now we finally have enough horsepower for some serious power flow control or motor drive algorithms.

Or do we?

The switching frequencies tend to go up, now even more with the proliferation of wide band-gap devices (GaN and SiC), which transition very fast and thus have low switching losses. Fast switching lowers the filtering requirements (why? filter store energy and the faster the energy cycle, the smaller the energy requirement, hence the need for lower inductances and capacitances). So there is a clear need for fast switching. Yes, the C2000 series processors have very fast PWM modules. But all we can do at these frequencies is to go through a simple control law (e.g. my article here). Assume 150 MHz clock F28335 (my favorite processor for quick development) and assume a 200 kHz switching frequency. That leaves us with 150e6/0.2e6 = 300 instructions per interrupt. That is really just enough to calculate a more complicated control law with some filtering. Observers, estimators? No way...

Motor drives, on the other hand, tend to switch much slower. Why would that be? That's because the motor leakage and magnetizing inductances are given by the motor design. The current ripple is already held quite low because of these typically fairly large values. So there is really no great benefit of increasing the switching frequency above 20 kHz. But... motor drive control laws are getting increasingly complex. Think about these algorithms:

- High-frequency injection for position estimation

- Optimal switching direct-torque control

- Flux estimators using dynamic machine models

- Motor drive synchronization

- A number of forward and backward Park Transforms (trigonometric functions)

- ...

The F28335 processor gives us 150e6/20e3 = 7500 instructions per period. That's plenty for some of these algorithms but certainly not enough for all of them, unless the motor drive software designer uses very heavy optimization (which is time consuming).

Actually, why should one bother with code optimization? In all honesty, I spend a fair amount of my time optimizing various code. And that is not time well spent (bar some job security...). The way to move the technology forward is to have powerful embedded platforms capable of handling any amount of fancy control code. The more time is spent on algorithm development the better for the designer and the company*. I am sure you know the old trick of estimating spare interrupt time- simply set a free IO at the beginning an interrupt and clear the IO at the end of the interrupt. And I am also sure that you have been in the situation where the there is almost no time left and the code is not near completion.

* R&D requirements are quite different from product development. More horsepower typically results in higher cost.

FPGA to the rescue

The beauty of FPGA comes in the absolute modularity. We can define (and we often do) special modulation schemes as an IP block, define our communication protocols to connect with reasonably performing A-to-D converters (large systems do rarely use instantaneous sampling) and then calculate control laws and other using the remaining logic fabric. And even though FPGA clocking frequencies do not go to the GHz range, FPGA can easily make up the clocking performance by exploiting the hardware parallelism and scalability. Do you need to add two 16-bit numbers in one cycle? No problem. Do you need to add two 40-bit numbers in one cycle? No problem as well, just use more logic elements. Are there five additions of independent variables (done sequentially on a processor), we can do all five here in one cycle. And this is the music of the future, at least for demanding power conversion control schemes.

Still, FGPAs are not all so rosy. The downside is the compilation time, even though this has been recently alleviated by partial synthesization and the use of hard ARM cores resulting in a hybrid System-on-a -chip solution.

Is there a victory to be declared?

The conclusion is somewhat less poetic and absolute that one would hope for- there is no clear winner as there will always be markets for simple 8-bit (~tens of cents), 16-bit (~dollar), and 32-bit processors (~dollars) as well as low-end FPGAs (~dollars) all the way to high-end Virtex (which can be thousands of dollars). Still, for me personally and for advanced power electronics and motor controls the winners are:

- System on a chip

- Fast FPGA

- FPGA + DSP

And that's all for today, folks.

Further Reading

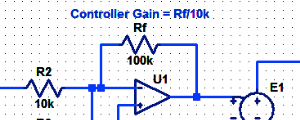

Proportional Controller Implementation

In MatLab, DSPs, and FPGAs.

.

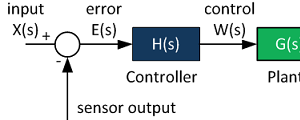

Control System Block Diagram

The fundamentals of signal flow.

System Modeling With Transfer Functions

Introduction to dynamic systems.

Fourier Series Demo

It is all sine waves.